- IC型号

企业档案

基于DS1302数字时钟电路的设计

发布时间: 2023/2/24 14:55:02 | 225 次阅读

从古代的滴漏更鼓到近代的机械钟,从电子表到目前的数字时钟,为了准确的测量和记录时间,人们一直在努力改良着计时工具。钟表的数字化,大力推动了计时的jing确性和可靠性。在单片机构成的装置中,实时时钟是必不可少的部件。目前常用的实时时钟,很多采用单片机的中断效劳来实现,这种方式一方面需要采用计数器,占用硬件资源,另一方面需要设置中断、查询等,同样消耗单片机的资源,而且某些测控系统可能不允许;有的那么使用并行接口的时钟芯片,如MC146818、DS12887等,它们虽然能满足单片机系统对实时时钟的要求,但是这些芯片与单片机接口复杂,占用地址、数据总线多,芯片体积大,占用空间多,给其它设计带来诸多不便。

本设计选取串行接口时钟芯片DS1302与单片机同步通信构成数字时钟电路。其简单的三线接口能为单片机节省大量资源,DS1302的后背电源及对后背电源进行涓细电流充电的能力保证电路断电后仍能保存时间和数据信息等。这些优点解决了目前常用的实时时钟所无法解决的问题。该时钟电路强大的功能和优越的性能,在很多领域的应用中,尤其是某些自动化控制、长时间无人看守的测控系统等对时钟jing确性和可靠性有较高要求的场合,具有很高的使用价值。

DS1302是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟芯片,它可以对年、月、日、周日、时、分、秒进行计时,且具有闰年补偿功能,工作电压宽达2.5~5.5V。时钟可工作在24小时格式或12小时〔AM/PM〕格式。DS1302与单片机的接口使用同步串行通信,仅用3条线与之相连接。可采用yi次传送一个字节或突发方式yi次传送多个字节的时钟信号或RAM数据。DS1302内部有一个31?8的用于临时性存放数据的RAM存放器。DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后背电源双电源引脚,同时提供了对后背电源进行涓细电流充电的能力。

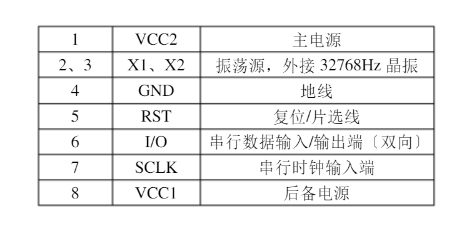

DS1302的引脚功能如表1所示,外形及内部结构如图1所示:

表1 DS1302引脚功能表

图1 DS1302管脚图及内部结构图

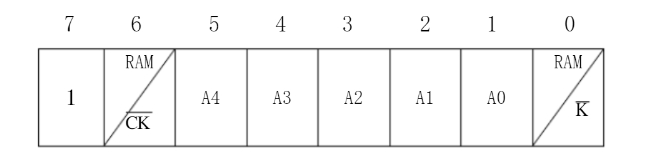

DS1302的控制字节如图2所示:

图2 DS1302控制字节的含义

控制字节的zui高有效位〔位7〕必须是逻辑1,如果它为0,那么不能把数据写入到DS1302中。位6如果为0,那么表示存取日历时钟数据,为1表示存取RAM数据;位5至位1指示操作单元的地址;zui低有效位〔位0〕如为0表示要进行写操作,为1表示进行读操作,控制字节总是从zui低位开始输出。

通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位存放器;其次RST提供了终止单字节或多字节数据的传送手段。当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中置RST为低电平,那么会终止此次数据传送,并且I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,必须保持RST低电平。只有在SCLK为低电平时,才能将RST置为高电。

在控制指令字输入后的下一个SCLK时钟的上升沿时数据被写入DS1302,数据输入从低位即位0开始。同样,在紧跟8位的控制指令字后的下一个SCLK脉冲的下降沿读出DS1302的数据,读出数据时从低位0位至高位7,数据读写时序如图3所示:

图3 数据读写时序

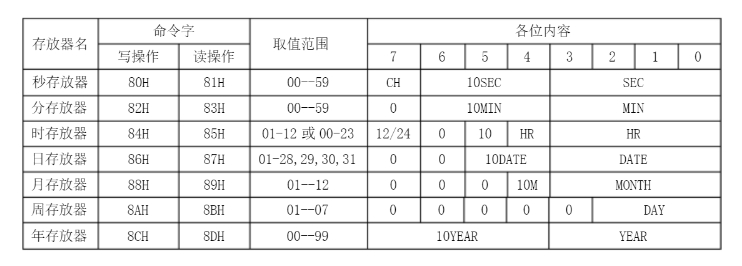

DS1302共有12个存放器,其中有7个存放器与日历、时钟相关,存放的数据位为BCD码形式。其日历、时间存放器及其控制字见表2。

此外,DS1302还有年份存放器、控制存放器、充电存放器、时钟突发存放器及与RAM相关的存放器等。时钟突发存放器可yi次性顺序读写除充电存放器外的所有存放器的内容。 DS1302与RAM相关的存放器分为两类,一类是单个RAM单元,共31个,每个单元组态为一个8位的字节,其命令控制字为C0H--FDH,其中奇数为读操作,偶数为写操作;再一类为突发方式下的RAM存放器,此方式下可yi次性读写所有的RAM的31个字节,命令控制字为FEH〔写〕、FFH〔读〕。

表2 DS1302的日历、时钟存放器及其控制字

该芯片还具有PDIP、TQFP和PLCC等三种封装形式,以适应不同产品的需求。

上一篇:保险丝用什么材料制作?